# SPECIFICATION FOR APPROVAL

| ( | ) Preliminary Specification |

|---|-----------------------------|

| ( | ) Final Specification       |

| T:11 = | 47 0" CVCA TET LCD   |

|--------|----------------------|

| LITIO  | 1/ U SX(3A IFI I (3) |

| BUYER | LGE |

|-------|-----|

| MODEL |     |

| SUPPLIER | LG.Philips LCD Co., Ltd. |

|----------|--------------------------|

| *MODEL   | LM170E03                 |

| SUFFIX   | TLL2                     |

<sup>\*</sup>When you obtain standard approval, please use the above model name without suffix

|   | SIGNATURE | DATE |

|---|-----------|------|

| _ | 1         |      |

|   |           |      |

| _ | 1         |      |

|   |           |      |

| _ | /         |      |

|   |           |      |

Please return 1 copy for your confirmation with

your signature and comments.

APPROVED BY

J. S. Cho / G.Manager

REVIEWED BY

S. U. Byun / Manager [C]

K. H. Moon / Manager [M]

D. Y. Seok / Manager [P]

PREPARED BY

K. H. Oh / Engineer

Product Engineering Dept.

LG. Philips LCD Co., Ltd

Ver 1.0 Jan. 22, 2007 1 / 28

## **CONTENTS**

| NO. | ITEM                         | Page |

|-----|------------------------------|------|

| -   | COVER                        | 1    |

| -   | CONTENTS                     | 2    |

| -   | RECORD OF REVISIONS          | 3    |

| 1   | GENERAL DESCRIPTION          | 4    |

| 2   | ABSOLUTE MAXIMUM RATINGS     | 5    |

| 3   | ELECTRICAL SPECIFICATIONS    | 6    |

| 3-1 | ELECTRICAL CHARACTERISTICS   | 6    |

| 3-2 | INTERFACE CONNECTIONS        | 8    |

| 3-3 | SIGNAL TIMING SPECIFICATIONS | 12   |

| 3-4 | SIGNAL TIMING WAVEFORMS      | 13   |

| 3-5 | COLOR INPUT DATA REFERANCE   | 14   |

| 3-6 | POWER SEQUENCE               | 15   |

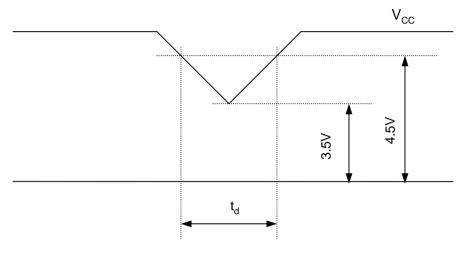

| 3-7 | VCC POWER DIP CONDITION      | 16   |

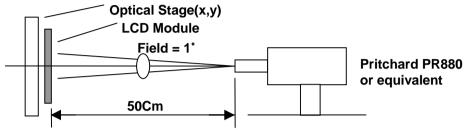

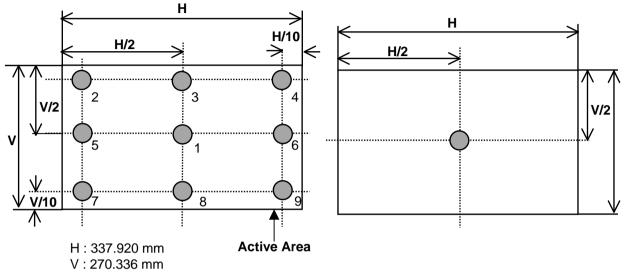

| 4   | OPTICAL SPECIFICATIONS       | 17   |

| 5   | MECHANICAL CHARACTERISTICS   | 21   |

| 6   | RELIABILITY                  | 24   |

| 7   | INTERNATIONAL STANDARDS      | 25   |

| 7-1 | SAFETY                       | 25   |

| 7-2 | EMC                          | 25   |

| 8   | PACKING                      | 26   |

| 8-1 | DESIGNATION OF LOT MARK      | 26   |

| 8-2 | PACKING FORM                 | 26   |

| 9   | PRECAUTIONS                  | 27   |

## **RECORD OF REVISIONS**

| Revision No | Date          | Page    | Description                                                                         |

|-------------|---------------|---------|-------------------------------------------------------------------------------------|

| Ver 0.1     | Dec. 12, 2006 |         | Preliminary Specification                                                           |

| Ver 1.0     | Jan. 22, 2007 | Page 4  | Update For Power Consumption                                                        |

|             |               | Page 6  | Update For Power Supply Input Current & Power Consumption                           |

|             |               | Page 12 | Update For Signal Timing Specification<br>: Hsync Max Timing (952 → 1022)           |

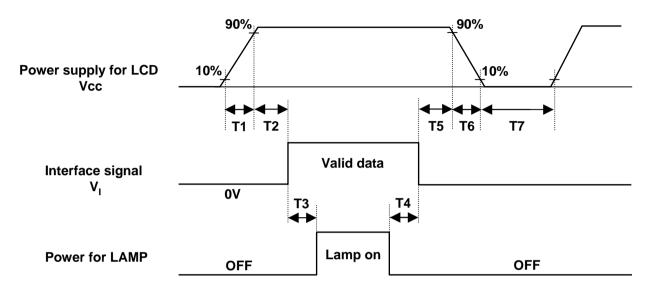

|             |               | Page 15 | Update For Power Sequence<br>: T3 Min. (500ms → 200ms)<br>: T6 Max. (10ms → 2000ms) |

|             |               |         | Final Specification                                                                 |

|             |               |         |                                                                                     |

|             |               |         |                                                                                     |

|             |               |         |                                                                                     |

|             |               |         |                                                                                     |

|             |               |         |                                                                                     |

|             |               |         |                                                                                     |

|             |               |         |                                                                                     |

|             |               |         |                                                                                     |

|             |               |         |                                                                                     |

|             |               |         |                                                                                     |

|             |               |         |                                                                                     |

|             |               |         |                                                                                     |

|             |               |         |                                                                                     |

### 1. General Description

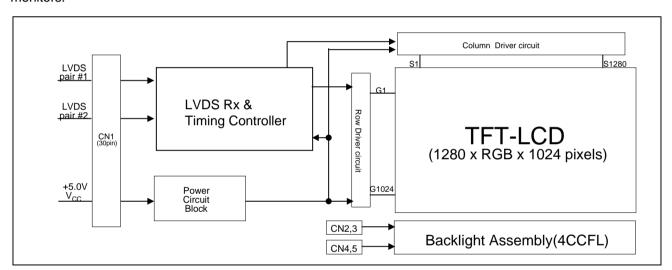

The LM170E03-TLL2 is a Color Active Matrix Liquid Crystal Display with an integral Cold Cathode Fluorescent Lamp(CCFL) backlight system. The matrix employs a-Si Thin Film Transistor as the active element. It is a transmissive type display operating in the normally white mode. This TFT-LCD has a 17.0 inch diagonal measured active display area with SXGA resolution(1024 vertical by 1280 horizontal pixel array) Each pixel is divided into Red, Green and Blue sub-pixels or dots which are arranged in vertical stripes. Gray scale or the brightness of the sub-pixel color is determined with a 8-bit gray scale signal for each dot, thus, presenting a palette of more than 16.7M colors with A-FRC(Advanced-Frame Rate Control).

The LM170E03-TLL2 has been designed to apply the interface method that enables low power, high speed,low EMI. FPD Link or compatible must be used as a LVDS(Low Voltage Differential Signaling) chip.

The LM170E03-TLL2 is intended to support applications where thin thickness, wide viewing angle, low power are critical factors and graphic displays are important. In combination with the vertical arrangement of the sub-pixels, the LM170E03-TLL2 characteristics provide an excellent flat panel display for office automation products such as monitors.

[ Figure 1 ] Block diagram

### **General Features**

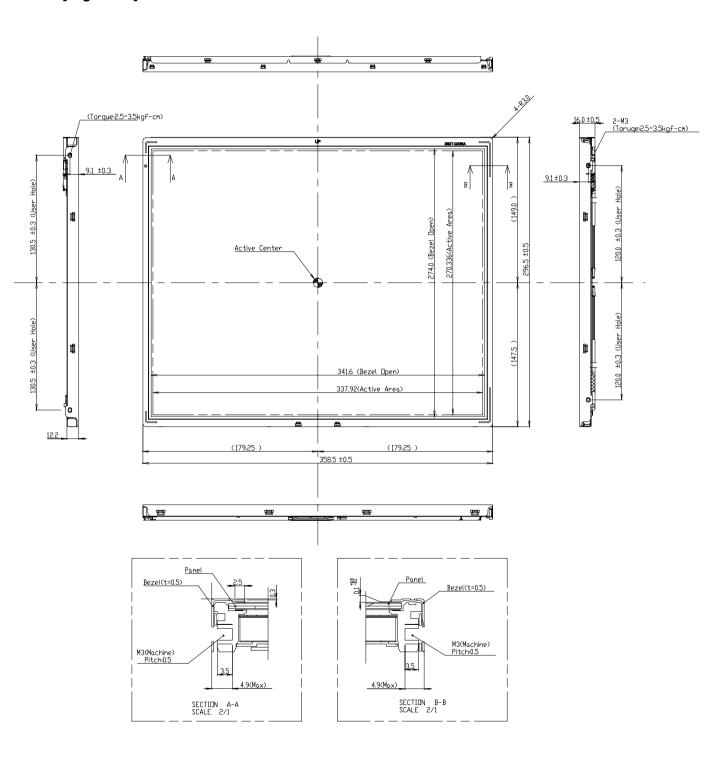

| Active screen size     | 17.0 inch (43.27cm) diagonal                                   |

|------------------------|----------------------------------------------------------------|

| Outline Dimension      | 358.5(H) x 296.5(V) x 16.0(D) mm(Typ.)                         |

| Pixel Pitch            | 0.264 mm x 0.264 mm                                            |

| Pixel Format           | 1280 horiz. by 1024 vert. Pixels. RGB stripe arrangement       |

| Display Colors         | 16.7M colors                                                   |

| Luminance, white       | 300 cd/m <sup>2</sup> (Typ. Center 1 point)                    |

| Power Consumption      | 21.1 Watts(Typ.)                                               |

| Weight                 | 1600g (Typ.)                                                   |

| Display operating mode | Transmissive mode, normally white                              |

| Surface treatments     | Hard coating (3H), Anti-glare treatment of the front polarizer |

## 2. Absolute maximum ratings

The following are maximum values which, if exceeded, may cause faulty operation or damage to the unit.

**Table 1. Absolute Maximum Ratings**

| Doromotor                                                                                                                    | Cumbal                                       | Valu                           | ıes                                   | Unito                         | Notes                     |

|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------|---------------------------------------|-------------------------------|---------------------------|

| Parameter                                                                                                                    | Symbol                                       | Min.                           | Max.                                  | Units                         | Notes                     |

| Power Supply Input Voltage<br>Operating Temperature<br>Storage Temperature<br>Operating Ambient Humidity<br>Storage Humidity | $V_{CC}$ $T_{OP}$ $T_{ST}$ $H_{OP}$ $H_{ST}$ | - 0.3<br>0<br>- 20<br>10<br>10 | + 5.5<br>+ 50<br>+ 60<br>+ 90<br>+ 90 | V <sub>dc</sub><br>%RH<br>%RH | At 25<br>1<br>1<br>1<br>1 |

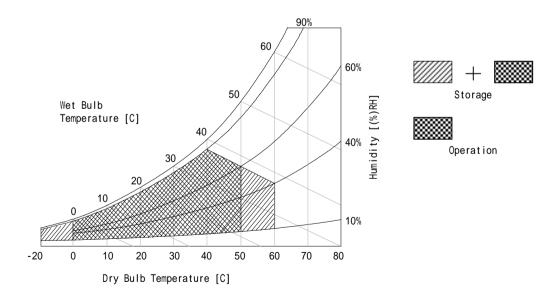

Note: 1. Temperature and relative humidity range are shown in the figure below.

Wet bulb temperature should be 39 °C Max, and no condensation of water.

[ Figure 2 ] Temperature and relative humidity

Ver 1.0 Jan. 22, 2007 5 / 28

Hrs

8

### **Product Specification**

### 3. Electrical specifications

Life Time

#### 3-1. Electrical characteristics

The LM170E03-TLL2 requires two power inputs. One is employed to power the LCD electronics and to drive the TFT array and liquid crystal. Another which powers the CCFL, is typically generated by an inverter. The inverter is an external unit to the LCD.

**Table 2. Electrical Characteristics**

| Parameter                     | Symbol            | Values   |          |          | Units     | Notes |

|-------------------------------|-------------------|----------|----------|----------|-----------|-------|

| Parameter                     | Зуньон            | Min.     | Тур.     | Max.     | Ullits    | Notes |

| MODULE :                      |                   |          |          |          |           |       |

| Power Supply Input Voltage    | $V_{CC}$          | 4.5      | 5.0      | 5.5      | V         |       |

| Permissive Power Input Ripple | $V_{RF}$          | -        | -        | 0.1      | V         |       |

| Power Supply Input Current    | I <sub>CC</sub>   | -        | 640      | 740      | mA        | 1     |

| Differential Impedance        | Zm                | 90       | 100      | 110      | ohm       |       |

| Power Consumption             | $P_{C}$           | -        | 3.2      | 3.7      | Watts     |       |

| Rush Current                  | I <sub>RUSH</sub> | -        | 2.0      | 3.0      | Α         | 2     |

| LAMP for each CCFL:           |                   |          |          |          |           |       |

| Operating Voltage             | $V_{BL}$          | 628      | 640      | 740      | $V_{RMS}$ | 3     |

|                               |                   | (@7.5mA) | (@7.0mA) | (@3.0mA) | Tavio     |       |

| Operating Current             | $I_BL$            | 3.0      | 7.0      | 7.5      | $mA_RMS$  |       |

| Established Starting Voltage  | $V_{BS}$          |          |          |          |           | 4     |

| at 25 °C                      |                   | -        | -        | 1000     | $V_{RMS}$ |       |

| at 0 °C                       |                   | -        | -        | 1250     | $V_{RMS}$ |       |

| Operating Frequency           | $f_{BL}$          | 40       | 60       | 70       | kHz       | 5     |

| Discharge Stabilization Time  | $T_S$             | -        | -        | 3        | Minutes   | 6     |

| Power Consumption             | $P_BL$            | -        | 17.90    | 19.70    | Watts     | 7     |

**Note.** The design of the inverter must have specifications for the lamp in LCD Assembly.

The performance of the Lamp in LCM, for example life time or brightness, is extremely influenced by the characteristics of the DC-AC Inverter. So all the parameters of an inverter should be carefully designed so as not to produce too much leakage current from high-voltage output of the inverter. When you design or order the inverter, please make sure unwanted lighting caused by the mismatch of the lamp and the inverter(no lighting, flicker, etc) never occurs. When you confirm it, the LCD Assembly should be operated in the same condition as installed in your instrument.

**Note.** Do not attach a conducting tape to lamp connecting wire. If the lamp wire attach to conducting tape, TFT-LCD Module have a low luminance and the inverter has abnormal action because leakage current occurs between lamp wire and conducting tape.

50,000

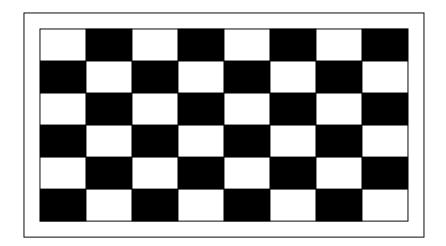

- 1. The specified current and power consumption are under the V<sub>CC</sub>=5.0V, 25°C, f<sub>V</sub>(frame frequency) =60Hz condition. Mosaic(black & white) pattern shown in the [Figure 3] is displayed.

- 2. The duration of rush current is about 5ms. And  $V_{CC}$  rise time is 500us  $\pm$  20%.

- Operating voltage is measured under 25 .The variance of the voltage is ± 10%.

- 4. The voltage above V<sub>BS</sub> should be applied to the lamps for more than 1 second for start-up. Otherwise, the lamps may not be turned on.

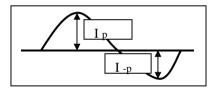

- 5. The output of the inverter must have symmetrical(negative and positive) voltage waveform and symmetrical current waveform. (Unsymmetrical ratio is less than 10%) Please do not use the inverter which has unsymmetrical voltage and unsymmetrical current and spike wave. Lamp frequency may produce interference with horizontal synchronous frequency and as a result this may cause beat on the display. Therefore lamp frequency shall be as away as possible from the horizontal synchronous frequency and from its harmonics in order to prevent interference.

- Let's define the brightness of the lamp after being lighted for 5 minutes as 100%.

T<sub>s</sub> is the time required for the brightness of the center of the lamp to be not less than 95%.

The used lamp current is the lamp typical current.

- 7. The lamp power consumption shown above does not include loss of external inverter under 25. The used lamp current is the lamp typical current.

- 8. The life time is determined as the time at which brightness of lamp is 50% compared to that of initial value at the typical lamp current on condition of continuous operating at  $25 \pm 2$ .

- Requirements for a system inverter design, which is intended to have a better display performance, a better power efficiency and a more reliable lamp.

- It shall help increase the lamp lifetime and reduce its leakage current.

- a. The unbalance rate of the inverter waveform should be 10% below;

- b. The distortion rate of the waveform should be within  $2 \pm 10\%$ ;

- c. The ideal sine wave form shall be symmetric in positive and negative polarities.

- \* Asymmetry rate =  $|I_p I_{-p}| / I_{rms}$  \* 100%

- \* Distortion rate =  $I_p$  (or  $I_{-p}$ ) /  $I_{rms}$

- 10. Inverter open voltage must be more than lamp starting voltage.

- 11. The inverter which is combined with this LCM, is highly recommended to connect coupling(ballast) condenser at the high voltage output side. When you use the inverter which has not coupling(ballast) condenser, it may cause abnormal lamp lighting because of biased mercury as time goes.

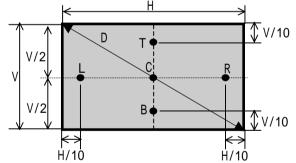

[ Figure 3 ] Mosaic pattern for power consumption measurement

### 3-2. Interface Connections

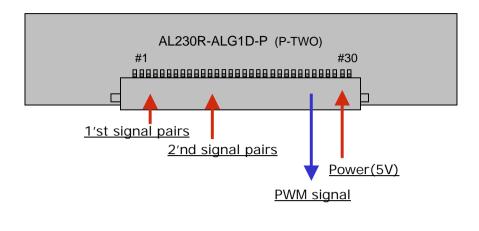

LCD Connector(CN1): AL230R-ALG1D-P (Manufactured by P-TWO)

or KDF71G-30S-1H (Manufactured by HIROSE)

or FI-X30SSL-HF (Manufactured by JAE) or GT103-30S-H23-M (Manufactured by LSC)

Mating Connector: FI-X30H and FI-X30HL (manufactured by JAE) or equivalent

Table 3. Module connector pin configuration

| Pin No | Symbol  | Description                                |                   |

|--------|---------|--------------------------------------------|-------------------|

| 1      | RxO0-   | LVDS Signal of Odd Channel 0(-)            |                   |

| 2      | RxO0+   | LVDS Signal of Odd Channel 0(+)            |                   |

| 3      | RxO1-   | LVDS Signal of Odd Channel 1(-)            |                   |

| 4      | RxO1+   | LVDS Signal of Odd Channel 1(+)            |                   |

| 5      | RxO2-   | LVDS Signal of Odd Channel 2(-)            |                   |

| 6      | RxO2+   | LVDS Signal of Odd Channel 2(+)            | First Pixel Data  |

| 7      | GND     | Ground                                     |                   |

| 8      | RxOC-   | LVDS Signal of Odd Channel Clock(-)        |                   |

| 9      | RxOC+   | LVDS Signal of Odd Channel Clock(+)        |                   |

| 10     | RxO3-   | LVDS Signal of Odd Channel 3(-)            |                   |

| 11     | RxO3+   | LVDS Signal of Odd Channel 3(+)            |                   |

| 12     | RxE0-   | LVDS Signal of Even Channel 0(-)           |                   |

| 13     | RxE0+   | LVDS Signal of Even Channel 0(+)           |                   |

| 14     | GND     | Ground                                     |                   |

| 15     | RxE1-   | LVDS Signal of Even Channel 1(-)           |                   |

| 16     | RxE1+   | LVDS Signal of Even Channel 1(+)           |                   |

| 17     | GND     | Ground                                     | Second Pixel Data |

| 18     | RxE2-   | LVDS Signal of Even Channel 2(-)           |                   |

| 19     | RxE2+   | LVDS Signal of Even Channel 2(+)           |                   |

| 20     | RxEC-   | LVDS Signal of Even Channel Clock(-)       |                   |

| 21     | RxEC+   | LVDS Signal of Even Channel Clock(+)       |                   |

| 22     | RxE3-   | LVDS Signal of Even Channel 3(-)           |                   |

| 23     | RxE3+   | LVDS Signal of Even Channel 3(+)           |                   |

| 24     | GND     | Ground                                     |                   |

| 25     | PWM_OUT | PWM_OUT signal for control burst frequence | cy of inverter    |

| 26     | NC      | No connection                              |                   |

| 27     | NC      | No connection                              |                   |

| 28     | VCC     | Power supply (5.0V Typ.)                   |                   |

| 29     | VCC     | Power supply (5.0V Typ.)                   |                   |

| 30     | VCC     | Power supply (5.0V Typ.)                   |                   |

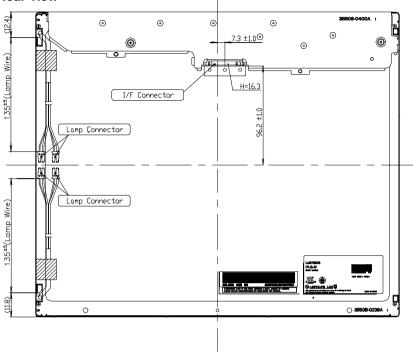

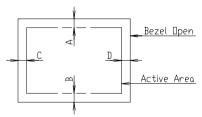

#### Rear view of LCM

#### [ Figure 4] Connector diagram

- Notes: 1. All GND(ground) pins should be connected together and should also be connected to the LCD's metal frame.

- 2. All V<sub>CC</sub>(power input) pins should be connected together.

- 3. All NC pins should be separated from other signal or power.

- 4. PWM\_OUT signal controls the burst frequency of a inverter. This signal is synchronized with vertical frequency, it's frequency is 3 times of vertical frequency, and it's duty ratio is 50%. If you don't use this pin, it is no connection.

Interface chip must be used LVDS, part No. SN75LVDS83 (Tx, Texas Instrument) or compatible.

Table 4. Required signal assignment for Flat Link (TI:SN75LVDS83) Transmitter

| VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Din | Pin Pin Name Require Signal Pin Pin Name Require Signal |                            |    |           |                                         |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------|----------------------------|----|-----------|-----------------------------------------|--|--|

| 2         D5         TTL Input(R7)         30         D26         TTL Input(DE)           3         D6         TTL Input(R5)         31         TxCLKIN         TTL Level clock Input           4         D7         TTL Input(G0)         32         PWR DWN         Power Down Input           5         GND         Ground pin for TTL         33         PLL GND         Ground pin for PLL           6         D8         TTL Input(G1)         34         PLL VCC         Power Supply for PLL           7         D9         TTL Input(G2)         35         PLL GND         Ground pin for PLL           8         D10         TTL Input(G2)         36         LVDS GND         Ground pin for PLL           8         D10         TTL Input(G2)         36         LVDS GND         Ground pin for PLL           9         VCC         Power Supply for TTL Input         37         TxOUT3+         Positive LVDS differential data output3           10         D11         TTL Input(G3)         39         TxCLKOUT+         Positive LVDS differential clock output           11         D12         TTL Input(G4)         40         TxCLKOUT+         Positive LVDS differential data output2           14         D14         TTL Input(G5)                                                                                                                                                          |     | Pin Name                                                | Require Signal             |    | Pin Name  | Require Signal                          |  |  |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1   | VCC                                                     | Power Supply for TTL Input | 29 | GND       | Ground pin for TTL                      |  |  |

| 4         D7         TTL Input(G0)         32         PWR DWN         Power Down Input           5         GND         Ground pin for TTL         33         PLL GND         Ground pin for PLL           6         D8         TTL Input(G1)         34         PLL VCC         Power Supply for PLL           7         D9         TTL Input(G6)         36         LVDS GND         Ground pin for LVDS           8         D10         TTL Input(G6)         36         LVDS GND         Ground pin for LVDS           9         VCC         Power Supply for TTL Input         37         TXOUT3+         Positive LVDS differential data output3           10         D11         TTL Input(G7)         38         TXOUT3-         Negative LVDS differential data output3           11         D12         TTL Input(G3)         39         TXCLKOUT-         Positive LVDS differential clock output           12         D13         TTL Input(G4)         40         TXCLKOUT-         Negative LVDS differential clock output           13         GND         Ground pin for TTL         41         TXOUT2-         Positive LVDS differential data output2           14         D14         TTL Input(B5)         42         TXOUT2-         Negative LVDS differential data output2                                                                                                                        | 2   | D5                                                      | TTL Input(R7)              | 30 | D26       | TTL Input(DE)                           |  |  |

| 5         GND         Ground pin for TTL         33         PLL GND         Ground pin for PLL           6         D8         TTL Input(G1)         34         PLL VCC         Power Supply for PLL           7         D9         TTL Input(G2)         35         PLL GND         Ground pin for PLL           8         D10         TTL Input(G6)         36         LVDS GND         Ground pin for LVDS           9         VCC         Power Supply for TTL Input         37         TXOUT3+         Positive LVDS differential data output3           10         D11         TTL Input(G7)         38         TXCLKOUT-         Negative LVDS differential clock output           11         D12         TTL Input(G3)         39         TXCLKOUT-         Negative LVDS differential clock output           12         D13         TTL Input(G4)         40         TXCLKOUT-         Negative LVDS differential clock output           13         GND         Ground pin for TTL         41         TXOUT2+         Positive LVDS differential clock output           14         D14         TTL Input(G5)         42         TXOUT2-         Negative LVDS differential data output2           15         D15         TTL Input(B6)         44         LVDS VCC         Power Supply for LVDS </td <td>3</td> <td>D6</td> <td>TTL Input(R5)</td> <td>31</td> <td>TxCLKIN</td> <td>TTL Level clock Input</td> | 3   | D6                                                      | TTL Input(R5)              | 31 | TxCLKIN   | TTL Level clock Input                   |  |  |

| D8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4   | D7                                                      | TTL Input(G0)              | 32 | PWR DWN   | Power Down Input                        |  |  |

| 7         D9         TTL Input(G2)         35         PLL GND         Ground pin for PLL           8         D10         TTL Input(G6)         36         LVDS GND         Ground pin for LVDS           9         VCC         Power Supply for TTL Input         37         TxOUT3+         Positive LVDS differential data output3           10         D11         TTL Input(G7)         38         TxOUT3-         Negative LVDS differential data output3           11         D12         TTL Input(G3)         39         TxCLKOUT+         Positive LVDS differential clock output           12         D13         TTL Input(G4)         40         TxCLKOUT-         Negative LVDS differential clock output           13         GND         Ground pin for TTL         41         TxOUT2+         Positive LVDS differential data output2           14         D14         TTL Input(B5)         42         TxOUT2-         Negative LVDS differential data output2           15         D15         TTL Input(B0)         43         LVDS VCC         Power Supply for LVDS           16         D16         TTL Input(B6)         44         LVDS VCC         Power Supply for LVDS           17         VCC         Power Supply for TTL Input         45         TxOUT1+         Positive LVDS diffe                                                                                                    | 5   | GND                                                     | Ground pin for TTL         | 33 | PLL GND   | Ground pin for PLL                      |  |  |

| 8         D10         TTL Input(G6)         36         LVDS GND         Ground pin for LVDS           9         VCC         Power Supply for TTL Input         37         TxOUT3+         Positive LVDS differential data output3           10         D11         TTL Input(G7)         38         TxOUT3-         Negative LVDS differential data output3           11         D12         TTL Input(G3)         39         TxCLKOUT+         Positive LVDS differential clock output           12         D13         TTL Input(G4)         40         TxCLKOUT-         Negative LVDS differential clock output           13         GND         Ground pin for TTL         41         TxOUT2+         Positive LVDS differential data output2           14         D14         TTL Input(G5)         42         TxOUT2-         Negative LVDS differential data output2           15         D15         TTL Input(B0)         43         LVDS VCC         Power Supply for LVDS           16         D16         TTL Input(B1)         45         TxOUT1+         Positive LVDS differential data output1           18         D17         TTL Input(B7)         46         TxOUT1+         Negative LVDS differential data output1           19         D18         TTL Input(B1)         47         TxOUT0+                                                                                                     | 6   | D8                                                      | TTL Input(G1)              | 34 | PLL VCC   | Power Supply for PLL                    |  |  |

| 9         VCC         Power Supply for TTL Input         37         TxOUT3+         Positive LVDS differential data output3           10         D11         TTL Input(G7)         38         TxOUT3-         Negative LVDS differential data output3           11         D12         TTL Input(G3)         39         TxCLKOUT-         Positive LVDS differential clock output           12         D13         TTL Input(G4)         40         TxCLKOUT-         Negative LVDS differential clock output           13         GND         Ground pin for TTL         41         TxOUT2+         Positive LVDS differential data output2           14         D14         TTL Input(G5)         42         TxOUT2-         Negative LVDS differential data output2           15         D15         TTL Input(B0)         43         LVDS GND         Ground pin for LVDS           16         D16         TTL Input(B6)         44         LVDS VCC         Power Supply for LVDS           17         VCC         Power Supply for TTL Input         45         TxOUT1+         Positive LVDS differential data output1           18         D17         TTL Input(B1)         47         TxOUT0+         Positive LVDS differential data output1           19         D18         TTL Input(B2)         48         TxO                                                                                           | 7   | D9                                                      | TTL Input(G2)              | 35 | PLL GND   | Ground pin for PLL                      |  |  |

| D11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8   | D10                                                     | TTL Input(G6)              | 36 | LVDS GND  | Ground pin for LVDS                     |  |  |

| 11         D12         TTL Input(G3)         39         TxCLKOUT+         Positive LVDS differential clock output           12         D13         TTL Input(G4)         40         TxCLKOUT-         Negative LVDS differential clock output           13         GND         Ground pin for TTL         41         TxOUT2+         Positive LVDS differential data output2           14         D14         TTL Input(G5)         42         TxOUT2-         Negative LVDS differential data output2           15         D15         TTL Input(B0)         43         LVDS GND         Ground pin for LVDS           16         D16         TTL Input(B6)         44         LVDS VCC         Power Supply for LVDS           17         VCC         Power Supply for TTL Input         45         TxOUT1+         Positive LVDS differential data output1           18         D17         TTL Input(B7)         46         TxOUT1-         Negative LVDS differential data output1           19         D18         TTL Input(B1)         47         TxOUT0+         Positive LVDS differential data output0           20         D19         TTL Input(B2)         48         TxOUT0-         Negative LVDS differential data output0           21         GND         Ground pin for TTL Input         49         LVDS                                                                                           | 9   | VCC                                                     | Power Supply for TTL Input | 37 | TxOUT3+   | Positive LVDS differential data output3 |  |  |

| 12         D13         TTL Input(G4)         40         TxCLKOUT-         Negative LVDS differential clock output           13         GND         Ground pin for TTL         41         TxOUT2+         Positive LVDS differential data output2           14         D14         TTL Input(G5)         42         TxOUT2-         Negative LVDS differential data output2           15         D15         TTL Input(B0)         43         LVDS GND         Ground pin for LVDS           16         D16         TTL Input(B6)         44         LVDS VCC         Power Supply for LVDS           17         VCC         Power Supply for TTL Input         45         TxOUT1+         Positive LVDS differential data output1           18         D17         TTL Input(B7)         46         TxOUT0+         Positive LVDS differential data output1           19         D18         TTL Input(B1)         47         TxOUT0+         Positive LVDS differential data output0           20         D19         TTL Input(B2)         48         TxOUT0-         Negative LVDS differential data output0           21         GND         Ground pin for TTL Input         49         LVDS GND         Ground pin for TTL           22         D20         TTL Input(B3)         50         D27         TTL I                                                                                                    | 10  | D11                                                     | TTL Input(G7)              | 38 | TxOUT3-   | Negative LVDS differential data output3 |  |  |

| 13         GND         Ground pin for TTL         41         TxOUT2+         Positive LVDS differential data output2           14         D14         TTL Input(G5)         42         TxOUT2-         Negative LVDS differential data output2           15         D15         TTL Input(B0)         43         LVDS GND         Ground pin for LVDS           16         D16         TTL Input(B6)         44         LVDS VCC         Power Supply for LVDS           17         VCC         Power Supply for TTL Input         45         TXOUT1+         Positive LVDS differential data output1           18         D17         TTL Input(B7)         46         TXOUT1-         Negative LVDS differential data output1           19         D18         TTL Input(B1)         47         TXOUT0+         Positive LVDS differential data output0           20         D19         TTL Input(B2)         48         TXOUT0-         Negative LVDS differential data output0           21         GND         Ground pin for TTL Input         49         LVDS GND         Ground pin for TTL           22         D20         TTL Input(B3)         50         D27         TTL Input(R6)           23         D21         TTL Input(B5)         52         D1         TTL Input(R1)                                                                                                                             | 11  | D12                                                     | TTL Input(G3)              | 39 | TxCLKOUT+ | Positive LVDS differential clock output |  |  |

| 14         D14         TTL Input(G5)         42         TxOUT2-         Negative LVDS differential data output2           15         D15         TTL Input(B0)         43         LVDS GND         Ground pin for LVDS           16         D16         TTL Input(B6)         44         LVDS VCC         Power Supply for LVDS           17         VCC         Power Supply for TTL Input         45         TxOUT1+         Positive LVDS differential data output1           18         D17         TTL Input(B7)         46         TxOUT0-         Negative LVDS differential data output1           19         D18         TTL Input(B1)         47         TxOUT0+         Positive LVDS differential data output0           20         D19         TTL Input(B2)         48         TxOUT0-         Negative LVDS differential data output0           21         GND         Ground pin for TTL Input         49         LVDS GND         Ground pin for TTL           22         D20         TTL Input(B3)         50         D27         TTL Input(R6)           23         D21         TTL Input(B4)         51         D0         TTL Input(R1)           24         D22         TTL Input(RSVD)         53         GND         Ground pin for TTL           26                                                                                                                                            | 12  | D13                                                     | TTL Input(G4)              | 40 | TxCLKOUT- | Negative LVDS differential clock output |  |  |

| 15         D15         TTL Input(B0)         43         LVDS GND         Ground pin for LVDS           16         D16         TTL Input(B6)         44         LVDS VCC         Power Supply for LVDS           17         VCC         Power Supply for TTL Input         45         TxOUT1+         Positive LVDS differential data output1           18         D17         TTL Input(B7)         46         TxOUT1-         Negative LVDS differential data output1           19         D18         TTL Input(B1)         47         TxOUT0+         Positive LVDS differential data output0           20         D19         TTL Input(B2)         48         TxOUT0-         Negative LVDS differential data output0           21         GND         Ground pin for TTL Input         49         LVDS GND         Ground pin for TTL           22         D20         TTL Input(B3)         50         D27         TTL Input(R6)           23         D21         TTL Input(B4)         51         D0         TTL Input(R0)           24         D22         TTL Input(RSVD)         53         GND         Ground pin for TTL           26         VCC         Power Supply for TTL Input         54         D2         TTL Input(R2)           27         D24                                                                                                                                                  | 13  | GND                                                     | Ground pin for TTL         | 41 | TxOUT2+   | Positive LVDS differential data output2 |  |  |

| 16         D16         TTL Input(B6)         44         LVDS VCC         Power Supply for LVDS           17         VCC         Power Supply for TTL Input         45         TxOUT1+         Positive LVDS differential data output1           18         D17         TTL Input(B7)         46         TxOUT1-         Negative LVDS differential data output1           19         D18         TTL Input(B1)         47         TxOUT0+         Positive LVDS differential data output0           20         D19         TTL Input(B2)         48         TxOUT0-         Negative LVDS differential data output0           21         GND         Ground pin for TTL Input         49         LVDS GND         Ground pin for TTL           22         D20         TTL Input(B3)         50         D27         TTL Input(R6)           23         D21         TTL Input(B4)         51         D0         TTL Input(R0)           24         D22         TTL Input(B5)         52         D1         TTL Input(R1)           25         D23         TTL Input(RSVD)         53         GND         Ground pin for TTL           26         VCC         Power Supply for TTL Input         54         D2         TTL Input(R2)           27         D24         TTL I                                                                                                                                                | 14  | D14                                                     | TTL Input(G5)              | 42 | TxOUT2-   | Negative LVDS differential data output2 |  |  |

| 17         VCC         Power Supply for TTL Input         45         TxOUT1+         Positive LVDS differential data output1           18         D17         TTL Input(B7)         46         TxOUT1-         Negative LVDS differential data output1           19         D18         TTL Input(B1)         47         TxOUT0+         Positive LVDS differential data output0           20         D19         TTL Input(B2)         48         TxOUT0-         Negative LVDS differential data output0           21         GND         Ground pin for TTL Input         49         LVDS GND         Ground pin for TTL           22         D20         TTL Input(B3)         50         D27         TTL Input(R6)           23         D21         TTL Input(B4)         51         D0         TTL Input(R0)           24         D22         TTL Input(B5)         52         D1         TTL Input(R1)           25         D23         TTL Input(RSVD)         53         GND         Ground pin for TTL           26         VCC         Power Supply for TTL Input         54         D2         TTL Input(R2)           27         D24         TTL Input(HSYNC)         55         D3         TTL Input(R3)                                                                                                                                                                                                  | 15  | D15                                                     | TTL Input(B0)              | 43 | LVDS GND  | Ground pin for LVDS                     |  |  |

| 18         D17         TTL Input(B7)         46         TxOUT1-         Negative LVDS differential data output1           19         D18         TTL Input(B1)         47         TxOUT0+         Positive LVDS differential data output0           20         D19         TTL Input(B2)         48         TxOUT0-         Negative LVDS differential data output0           21         GND         Ground pin for TTL Input         49         LVDS GND         Ground pin for TTL           22         D20         TTL Input(B3)         50         D27         TTL Input(R6)           23         D21         TTL Input(B4)         51         D0         TTL Input(R0)           24         D22         TTL Input(B5)         52         D1         TTL Input(R1)           25         D23         TTL Input(RSVD)         53         GND         Ground pin for TTL           26         VCC         Power Supply for TTL Input         54         D2         TTL Input(R2)           27         D24         TTL Input(HSYNC)         55         D3         TTL Input(R3)                                                                                                                                                                                                                                                                                                                                         | 16  | D16                                                     | TTL Input(B6)              | 44 | LVDS VCC  | Power Supply for LVDS                   |  |  |

| 19         D18         TTL Input(B1)         47         TxOUT0+         Positive LVDS differential data output0           20         D19         TTL Input(B2)         48         TxOUT0-         Negative LVDS differential data output0           21         GND         Ground pin for TTL Input         49         LVDS GND         Ground pin for TTL           22         D20         TTL Input(B3)         50         D27         TTL Input(R6)           23         D21         TTL Input(B4)         51         D0         TTL Input(R0)           24         D22         TTL Input(B5)         52         D1         TTL Input(R1)           25         D23         TTL Input(RSVD)         53         GND         Ground pin for TTL           26         VCC         Power Supply for TTL Input         54         D2         TTL Input(R2)           27         D24         TTL Input(HSYNC)         55         D3         TTL Input(R3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17  | vcc                                                     | Power Supply for TTL Input | 45 | TxOUT1+   | Positive LVDS differential data output1 |  |  |

| 20         D19         TTL Input(B2)         48         TxOUT0-         Negative LVDS differential data output0           21         GND         Ground pin for TTL Input         49         LVDS GND         Ground pin for TTL           22         D20         TTL Input(B3)         50         D27         TTL Input(R6)           23         D21         TTL Input(B4)         51         D0         TTL Input(R0)           24         D22         TTL Input(B5)         52         D1         TTL Input(R1)           25         D23         TTL Input(RSVD)         53         GND         Ground pin for TTL           26         VCC         Power Supply for TTL Input         54         D2         TTL Input(R2)           27         D24         TTL Input(HSYNC)         55         D3         TTL Input(R3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18  | D17                                                     | TTL Input(B7)              | 46 | TxOUT1-   | Negative LVDS differential data output1 |  |  |

| 21         GND         Ground pin for TTL Input         49         LVDS GND         Ground pin for TTL           22         D20         TTL Input(B3)         50         D27         TTL Input(R6)           23         D21         TTL Input(B4)         51         D0         TTL Input(R0)           24         D22         TTL Input(B5)         52         D1         TTL Input(R1)           25         D23         TTL Input(RSVD)         53         GND         Ground pin for TTL           26         VCC         Power Supply for TTL Input         54         D2         TTL Input(R2)           27         D24         TTL Input(HSYNC)         55         D3         TTL Input(R3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19  | D18                                                     | TTL Input(B1)              | 47 | TxOUT0+   | Positive LVDS differential data output0 |  |  |

| 22         D20         TTL Input(B3)         50         D27         TTL Input(R6)           23         D21         TTL Input(B4)         51         D0         TTL Input(R0)           24         D22         TTL Input(B5)         52         D1         TTL Input(R1)           25         D23         TTL Input(RSVD)         53         GND         Ground pin for TTL           26         VCC         Power Supply for TTL Input         54         D2         TTL Input(R2)           27         D24         TTL Input(HSYNC)         55         D3         TTL Input(R3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20  | D19                                                     | TTL Input(B2)              | 48 | TxOUT0-   | Negative LVDS differential data output0 |  |  |

| 23         D21         TTL Input(B4)         51         D0         TTL Input(R0)           24         D22         TTL Input(B5)         52         D1         TTL Input(R1)           25         D23         TTL Input(RSVD)         53         GND         Ground pin for TTL           26         VCC         Power Supply for TTL Input         54         D2         TTL Input(R2)           27         D24         TTL Input(HSYNC)         55         D3         TTL Input(R3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21  | GND                                                     | Ground pin for TTL Input   | 49 | LVDS GND  | Ground pin for TTL                      |  |  |

| 24         D22         TTL Input(B5)         52         D1         TTL Input(R1)           25         D23         TTL Input(RSVD)         53         GND         Ground pin for TTL           26         VCC         Power Supply for TTL Input         54         D2         TTL Input(R2)           27         D24         TTL Input(HSYNC)         55         D3         TTL Input(R3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22  | D20                                                     | TTL Input(B3)              | 50 | D27       | TTL Input(R6)                           |  |  |

| 25         D23         TTL Input(RSVD)         53         GND         Ground pin for TTL           26         VCC         Power Supply for TTL Input         54         D2         TTL Input(R2)           27         D24         TTL Input(HSYNC)         55         D3         TTL Input(R3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23  | D21                                                     | TTL Input(B4)              | 51 | D0        | TTL Input(R0)                           |  |  |

| 26 VCC Power Supply for TTL Input 54 D2 TTL Input(R2)  27 D24 TTL Input(HSYNC) 55 D3 TTL Input(R3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24  | D22                                                     | TTL Input(B5)              | 52 | D1        | TTL Input(R1)                           |  |  |

| 27 D24 TTL Input(HSYNC) 55 D3 TTL Input(R3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25  | D23                                                     | TTL Input(RSVD)            | 53 | GND       | Ground pin for TTL                      |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26  | vcc                                                     | Power Supply for TTL Input | 54 | D2        | TTL Input(R2)                           |  |  |

| 28         D25         TTL Input(VSYNC)         56         D4         TTL Input(R4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27  | D24                                                     | TTL Input(HSYNC)           | 55 | D3        | TTL Input(R3)                           |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28  | D25                                                     | TTL Input(VSYNC)           | 56 | D4        | TTL Input(R4)                           |  |  |

Notes: 1. Refer to LVDS Transmitter Data Sheet for detail descriptions.

2. 7 means MSB and 0 means LSB at R,G,B pixel data

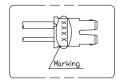

The backlight interface connector is a model 35001HS-02LD(YEONHO).

The mating connector part number is 35001WR-02L or equivalent.

The pin configuration for the connector is shown in the table 5.

Table 5. Backlight connector pin configuration

| Pin | Symbol | Description           | Notes |

|-----|--------|-----------------------|-------|

| 1   | HV     | High Voltage for lamp | 1     |

| 2   | LV     | Low Voltage for lamp  | 1,2   |

Notes: 1. The high voltage side terminal is colored white or pink. The low voltage side terminal is white or Blue.

2. The backlight ground should be common with LCD metal frame.

[ Figure 5 ] Backlight connector view

## 3-3. Signal Timing Specifications

This is the signal timing required at the input of the LVDS Transmitter. All of the interface signal timing should be satisfied with the following specifications for it's proper operation.

Table 6. Timing table

|                  | Parameter              | Symbol           | Min. | Тур. | Max. | Unit             | Notes                |

|------------------|------------------------|------------------|------|------|------|------------------|----------------------|

| D <sub>CLK</sub> | Period                 | t <sub>CLK</sub> | 14.6 | 18.5 | 22.2 | ns               |                      |

|                  | Frequency              | f <sub>CLK</sub> | 45   | 54   | 68   | MHz              |                      |

| Hsync            | Period                 | t <sub>HP</sub>  | 688  | 844  | 1022 | _                | Horizontal period    |

|                  | Width                  | t <sub>WH</sub>  | 16   | 56   | -    | t <sub>CLK</sub> | should be even       |

| Vsync            | Period                 | t <sub>VP</sub>  | 1032 | 1066 | 1536 |                  |                      |

|                  | Width                  | t <sub>VW</sub>  | 2    | 3    | 24   | t <sub>HP</sub>  |                      |

|                  | Frequency              | f <sub>V</sub>   | 50   | 60   | 76   | Hz               |                      |

| DE               | Horizontal Valid       | t <sub>HV</sub>  | 640  | 640  | 640  |                  |                      |

| (Data<br>Enable) | Horizontal Back Porch  | t <sub>HBP</sub> | 16   | 124  | -    | _                |                      |

| ,                | Horizontal Front Porch | t <sub>HFP</sub> | 8    | 24   | -    | t <sub>CLK</sub> |                      |

|                  |                        |                  | -    | -    | -    |                  |                      |

|                  | Vertical Valid         | t <sub>VV</sub>  | 1024 | 1024 | 1024 |                  |                      |

|                  | Vertical Back Porch    | t <sub>VBP</sub> | 5    | 38   | 124  | 4                |                      |

|                  | Vertical Front Porch   | t <sub>VFP</sub> | 1    | 1    | -    | t <sub>HP</sub>  |                      |

|                  |                        | -                | -    | -    | -    |                  |                      |

|                  | DE Setup Time          | t <sub>SI</sub>  | 4    | -    | -    |                  | For D <sub>CLK</sub> |

|                  | DE Hold Time           | t <sub>HI</sub>  | 4    | -    | -    | ns               |                      |

| Data             | Data Setup Time        | t <sub>SD</sub>  | 4    | -    | -    | no               | For D <sub>CLK</sub> |

|                  | Data Hold Time         | t <sub>HD</sub>  | 4    | -    | -    | ns               |                      |

Notes: 1. DE Only mode operation

- 2.  $t_{HFP} + t_{WH} + t_{HBP} < (1/2) t_{HV}$

- 3.  $t_{VFP}$  +  $t_{WV}$  +  $t_{VBP}$  <  $t_{H_{max}}/t_{v_{min}}$

- 4. tHFP, tWH and tHBP should be any times of a character number (8).

- 5. No variation of the total number of Hsync and DE in a frame is required for normal operation.

- 6. No variation of the total number of clock in a Hsync period for  $t_{VBP}$  is required for normal operation.

Ver 1.0 Jan. 22, 2007 12 / 28

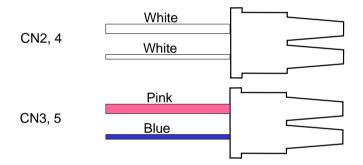

## 3-4. Signal Timing Waveforms

[ Figure 6 ] Signal timing waveforms

## 3-5. Color Input Data Reference

The brightness of each primary color(red,green and blue) is based on the 8-bit gray scale data input for the color; the higher the binary input, the brighter the color. The table below provides a reference for color versus data input.

Table 7. Color data reference

|                 |                                                                                                 |                                 |                                 |                                 |                                 |                                 |                            |                                 |                                 |                                 |                                 | Inp                             | ut (                            | colo                            | or d                            | lata                            | l                               |                                 |                                 |                            |                                 |                            |                                 |                                 |                            |

|-----------------|-------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|----------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|----------------------------|---------------------------------|----------------------------|---------------------------------|---------------------------------|----------------------------|

|                 | Color                                                                                           | Red<br>MSB                      |                                 |                                 |                                 |                                 | Green LSB MSB LSB          |                                 |                                 |                                 |                                 |                                 | S B                             | Blue<br>MSB LSB                 |                                 |                                 |                                 |                                 |                                 |                            |                                 |                            |                                 |                                 |                            |

|                 |                                                                                                 | R7                              |                                 | R5                              | R4                              | R3                              | R2                         | R1                              |                                 | G7                              | G6                              | G5                              | G4                              | G3                              | G2                              |                                 |                                 | B7                              | B6                              | B5                         | B4                              | ВЗ                         | B2                              | B1                              | В0                         |

| Basic<br>colors | Black Red(255) Green(255) Blue(255) Cyan Magenta Yellow White                                   | 0<br>1<br>0<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>0<br>1<br>1      | 0<br>0<br>1<br>0<br>1<br>0<br>1 | 0<br>0<br>0<br>1<br>1<br>1<br>0 | 0<br>0<br>0<br>1<br>1<br>1<br>0 | 0<br>0<br>1<br>1<br>1<br>0 | 0<br>0<br>0<br>1<br>1<br>1<br>0 | 0<br>0<br>1<br>1<br>1<br>0 | 0<br>0<br>1<br>1<br>1<br>0      | 0<br>0<br>0<br>1<br>1<br>1<br>0 | 0<br>0<br>1<br>1<br>1<br>0 |

| Red             | Red(000) dark<br>Red(001)<br>Red(002)<br>:<br>Red(253)<br>Red(254)<br>Red(255) bright           | 0<br>0<br>0<br>:<br>1<br>1      | 0<br>0<br>0<br>:<br>1<br>1      | 0<br>0<br>0<br>:<br>1<br>1      | 0<br>0<br>0<br>:<br>1<br>1      | 0<br>0<br>0<br>:<br>1<br>1      | 0<br>0<br>0<br>:<br>1<br>1 | 0<br>0<br>1<br>:<br>0<br>1      | 0<br>1<br>0<br>:<br>1<br>0<br>1 | 0<br>0<br>0<br>:<br>0<br>0      | 0 0 0 : 0 0 0                   | 0 0 : 0 0                       | 0<br>0<br>0<br>:<br>0<br>0      | 0 0 0 : 0 0                     | 0 0 0 : 0 0                     | 0 0 0 : 0 0                     | 0 0 0 : 0 0                     | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0 | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0 | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0 |

| Green           | Green(000)dark<br>Green(001)<br>Green(002)<br>:<br>Green(253)<br>Green(254)<br>Green(255)bright | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0 | 0<br>0<br>0<br>:<br>0<br>0      | 0 0 0 0 0                       | 0<br>0<br>0<br>:<br>1<br>1      | 0<br>0<br>0<br>:<br>1<br>1      | 0<br>0<br>0<br>:<br>1<br>1      | 0<br>0<br>0<br>:<br>1<br>1      | 0<br>0<br>0<br>:<br>1<br>1      | 0<br>0<br>0<br>:<br>1<br>1      | 0<br>0<br>1<br>:<br>0<br>1      | 0<br>1<br>0<br>:<br>1<br>0      | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0 | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0 | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0 |

| Blue            | Blue(000) dark<br>Blue(001)<br>Blue(002)<br>:<br>Blue(253)<br>Blue(254)<br>Blue(255) bright     | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0 | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0      | 0 0 0 : 0 0 0                   | 0<br>0<br>0<br>:<br>0<br>0      | 0<br>0<br>0<br>:<br>0<br>0      | 0 0 0 : 0 0                     | 0<br>0<br>0<br>:<br>0<br>0      | 0 0 0 : 0 0                     | 0 0 0 : 0 0                     | 0<br>0<br>0<br>:<br>1<br>1      | 0<br>0<br>0<br>:<br>1<br>1      | 0<br>0<br>0<br>:<br>1<br>1 | 0<br>0<br>0<br>:<br>1<br>1      | 0<br>0<br>0<br>:<br>1<br>1 | 0<br>0<br>0<br>:<br>1<br>1<br>1 | 0<br>0<br>1<br>:<br>0<br>1<br>1 | 0<br>1<br>0<br>:<br>1<br>0 |

### 3-6. Power Sequence

[ Figure 7 ] Power sequence

Table 8. Power sequence time delay

| Danamatan      |      | Values |      |       |  |  |  |  |  |

|----------------|------|--------|------|-------|--|--|--|--|--|

| Parameter      | Min. | Тур.   | Max. | Units |  |  |  |  |  |